|

| Freescale's B4860 provides a complete basestation on a chip for LTE and LTE-Advanced macrocells |

With their announcement of the B4860 at Mobile World Congress, Freescale Semiconductor is extending their line of QorIQ Qonverge basestation on a chip SOCs from picocells up through to large macro cells. In August of last year, Freescale began sampling their 45nm PSC9132/ 31/ 30 for femto and pico cells. The B4860, which Freescale will manufacture in a 28nm CMOS process, supports three 20MHz sectors of LTE, for metropolitan applications with hundreds or thousands of users.

Stephen Turnbull, Multicore & Host Processor Portfolio Manager at Freescale, says that the B4860 can achieve a download (DL) rate for LTE of 300Mbps, and an upload rate of 150Mbps. Turnbull also says that the macro basestation SOC is fully compliant with the 3rd Generation Partnership Project's (3GPP) Release 10 specification for LTE-Advanced, supporting 60MHz sectors at 1.2Gbps DL and 600Mbps UL, for a total data throughput of 1.8Gbps on Frequency Domain Duplexing FDD-LTE paired spectrum. The B4860 also supports WCDMA, TD-SCDMA, and GSM.

Freescale designed the B4860 for flexibility to support conventional Base-Band Units (BBU) at a macro cell site, for pooling of resources in a Cloud-based RAN (CRAN) connected to Remote Radio Heads (RRH) over Common Public Radio Interface (CPRI), or for use in heterogeneous networks with a mix of small and large cells.

Like other devices in the QorIQ family, such as the T4240 and T4160 for wireless backhaul applications, the B4860 architecture employs quad clusters of the dual-thread, 64-bit e6500 Power Architecture cores, along with the 128b AltiVec Single-Instruction Multiple-Data (SIMD) vector processor. This is the same architecture which Freescale simulations show to have achieved the highest CoreMark benchmark performance score ever recorded for an embedded processor.

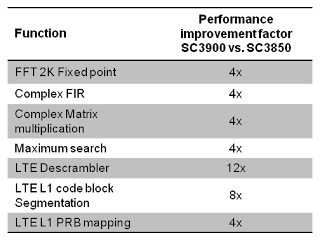

For baseband processing, the B4860 adopts a heterogeneous multi-core architecture, with three sets of dual StarCore SC3900 DSP cores, each pair sharing 2MB of L2 cache. Freescale benchmarks show the SC3900 DSP to provide 4X the performance of the previous generation SC3850, such as the cores in the PSC9132 basestation SOC for picocells. Freescale has announced that the SC3900 recently achieved the highest fixed-point BDTIsimMark2000™ benchmark score ever recorded by analysis firm Berkeley Design Technology, Inc. (BDTI). At 1.2 GHz, the SC3900 core registered a performance benchmark score of 37,460, which Freescale says is 2X higher than competitive DSPs on the market.

The Maple-B3 cores offload the DSPs to provide Layer-1 acceleration, and actually occupy a larger portion of the silicon real estate than the other cores, according to Turnbull. He says that the high level of integration provides the equivalent functionality of five components; 3 DSPs for Layer-1 processing, and a Serial RapidIO (SRIO) switch, connecting to a separate multicore processor for Layer-2 and Layer-3 transport and control processing. Freescale expects to begin sampling of QorIQ Qonverge B4860 devices in Q2 2012.

Related Articles

- Freescale gives an advanced look at 28nm, 64-bit multicore QorIQ design

- Freeescale claims highest ever CoreMark™ score with T4240 multicore processor, adds new T4160 to QorIQ AMP

- Freescale begins sampling basestation on a chip for femto and pico cells

- Will 4G wireless networks move basestations to the cloud?

No comments:

Post a Comment